## EIGER- short manual

## June 29, 2018

## Contents

| 1 | Usage                                                                | 1  |

|---|----------------------------------------------------------------------|----|

|   | 1.1 Short description                                                | 1  |

|   | 1.2 Mandatory setup - Hardware                                       | 1  |

|   | 1.2.1 9M power supply interface: bchip100                            | 3  |

|   | 1.3 Mandatory setup - Receiver                                       | 4  |

|   | 1.4 Mandatory setup - Client                                         | 5  |

| 2 | API versioning                                                       | 7  |

| 3 | Setting up the threshold                                             | 7  |

| 4 | Standard acquisition                                                 | 8  |

| 5 | Readout timing- maximum frame rate                                   | 9  |

|   | 5.1 Minimum time between frames and Maximum frame rate               | 10 |

|   | 5.1.1 4 and 8 bit mode                                               | 12 |

|   | 5.1.2 16 bit mode                                                    | 13 |

|   | 5.1.3 32 bit mode                                                    | 13 |

| 6 | External triggering options                                          | 14 |

| 7 | Autosumming and rate corrections                                     | 15 |

| 8 | Dependent parameters and limits                                      | 16 |

| 9 | $1 \mathrm{Gb/s}, 10 \mathrm{Gb/s}  \mathrm{links}$                  | 18 |

|   | 9.1 Checking the 1Gb/s, 10Gb/s physical links                        | 18 |

|   | 9.2 Delays in sending for 1Gb/s, 10Gb/s, 10Gb flow control, receiver |    |

|   | fifo                                                                 | 18 |

|   | 9.3 Setting up 10Gb correctly: experience so far                     | 20 |

| 10           | Offline processing and monitoring  10.1 Data out of the detector: UDP packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20<br>20<br>20<br>21<br>22<br>23                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| $\mathbf{A}$ | Kill the server, copy a new server, start the server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                                                                       |

| В            | Loading firmware bitfiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24                                                                                                       |

| $\mathbf{C}$ | Pulsing the detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>25</b>                                                                                                |

| D            | Load a noise pattern with shape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                                                                                       |

| E            | E.1 Cannot successfully finish an acquisition  E.1.1 Only master module return from acquisition  E.1.2 A few modules do not return from acquisition  E.2 No packets (or very little) are received  E.3 'Got Frame Number Zero from Firmware'  E.4 The module seems dead, no lights on BEBs, no IP addresses  E.5 The module seems powered but no IP addresses  E.6 Receiver cannot open socket  E.7 The client ignores the commands  E.8 Zmq socket is blocked  E.9 Client has shmget error  E.10 Measure the HV  E.11 The image now has a vertical line  E.12 The image now has more vertical lines  E.13 ssh to the boards takes long  E.14 Check firmware version installed on BEB  E.15 Check if half-module is a master, a slave, a top or a bottom  E.16 'Cannot connect to socket'  E.17 Detector server is not running  E.18 'Acquire has already started' error message  E.19 There is noise running the detector at high frame rate(4,8,16 bit) | 26<br>26<br>26<br>26<br>27<br>28<br>28<br>29<br>29<br>29<br>30<br>30<br>30<br>31<br>31<br>31<br>31<br>32 |

| $\mathbf{F}$ | Client checks - command line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>32</b>                                                                                                |

| $\mathbf{G}$ | Complete data out rate tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                                                                       |

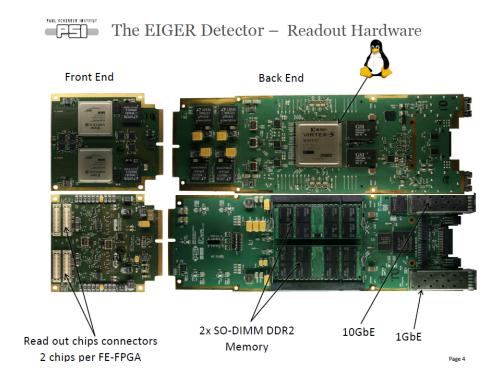

Figure 1: Picture with most relevant components of the EIGER readout system. The readout system starts with the Front End Boards (FEB) which performs data descrambling (also converts the packets from  $12 \rightarrow 16$  bits) and rate correction. The BackEndBoard (BEB) has 2x2GB DDR2 memories and can perform data buffering (storing images on board) and data summation (16 bit  $\rightarrow$  32 bits). The controls to the detector are passed through the 1Gb, while in most installations, the data are sent out through the 1GB ethernet connection.

## 1 Usage

#### 1.1 Short description

Figure 1 show the readout board basic components on an Eiger half module. An half module can read up to 4 readout chips.

#### 1.2 Mandatory setup - Hardware

An EIGER single module (500 kpixels) needs:

• A chilled (water+alcohol) at 21 °C for a single module (500k pixels), which needs to dissipate 85 W (every module, i.e. for two half boards). For the 9M, 1.5M, a special cooling liquid is required: 2/3 deionized water and 1/3

ESA Type 48. This is important as the high temperature generated by the boards accelerate the corrosion due to Cu/Al reaction and the blockage of the small channels where the liquid flows, in particular near the face of the detector and if it is a parallel flow and not a single loop. The 9M and 1.5M run at 19 °C.

- A power supply (12 V, 8 A). For the 9 M, a special cpu is give to remotely switch on and off the detector: see section 1.2.1.

- 2×1 Gb/s Ethernet connectors to control the detector and, optionally, receive data at low rate. A DHCP server that gives IPs to the 1 Gb/s connectors of the detector is needed. Note that flow control has to be enabled on the switch you are using, if you plan to read the data out from there. If not, you need to implement delays in the sending out of the data.

- 2×10 Gb/s transceivers to optionally, receive data at high rate. The 10Gb/s transceiver need to match the wavelength (long/short range) of the fibers chosen by the beamline infrastructure.

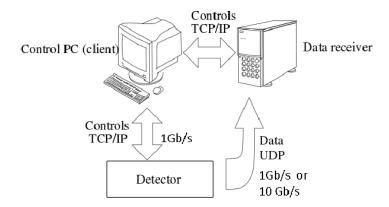

The equipment scales linearly with the number of modules. Figure 2 shows the relationship between the **Client** (which sits on a beamline control PC), the **Receiver** (which can run in multiple instances on one or more PCs which receive data from the detector. The receiver(s) does not necessary have to be running on the same PC as the client.) The username under which the receiver runs is the owner of the data files, if using our implementation. It is important that the receiver is closely connected to the detector (they have to be on the same network). Note that if you implement the 1Gb/s readout only: client, receiver and detector have to be all three in the same network. If you implement the 10Gb/s readout, then client, the 1 GbE of the detector and the receiver have to stay on the 1GbE. But the receiver data receiving device and the 10GbE detector can be on their private network, minimizing the missing packets.

The Client talks to control over 1 Gb Ethernet connection using TCP/IP to the detector and to the receiver. The detector sends data in UDP packets to the receiver. This data sending can be done over 1 Gb/s or 10 Gb/s.

- Switch on the detector only after having started the chiller: the 500k single module and the 1.5M at cSAXS/OMNY have a hardware temperature sensor, which will power off the boards if the temperature is too high. Note that the detector will be power on again as soon as the temperature has been lowered. The 9M will not boot up without the correct waterflow and temperature has it has an integrated flowmeter.

- Switch on the detector only after having connected all the cables and network. EIGER is unable to get IP address after it has been switched on without a proper network set up. In that case switch off and on the detector again.

Figure 2: Communications protocol between the Client PC, the receiver PC and the detector.

#### 1.2.1 9M power supply interface: bchip100

So the bchip100, which is a blackfin cpu, is located on the top side of the 9M and needs to be connected over 1Gb, to the same or a different network as the detector 1 GbE.

telnet bchip100 cd 9m/

The directory contains some executables that are needed to make your detector to work:

- ./on #to switch modules on

- ./off #to switch modules off

- ./hvget #gets the current HV value

- ./waterflow #returns the current waterflow returned by the flowmeter

- ./temp #returns the water temperature returned by the flowmeter

A watchdog is running on bchip100 to check for the flow and temperature. If outside of parameters ( flow< 80 dl/min, temperature  $\neq$ 21±2), the detector will be switched off. Here is an explanation of the LED color scheme of the bchip100:

- NO LED Main Power off or Blackfin not ready, yet.

- RED Too high temperature or too less water flow Detector is shut down and locked. Detector will be unlocked (YELLOW) automatically when conditions are good again.

- YELLOW Detector is off and unlocked. Ready to be turned on.

- GREEN Detector is on

You can also Check temperatures and water flow in a browser (from the same subnet where the 9M is: http://bchip100/status.cgi

#### 1.3 Mandatory setup - Receiver

The receiver is a process run on a PC closely connected to the detector. Open one receiver for every half module board (remember, a module has two receivers!!!) . Go to slsDetectorsPackage/build/bin/, slsReceiver should be started on the machine expected to receive the data from the detector.

- ./slsReceiver --rx\_tcpport xxxx

- ./slsReceiver --rx\_tcpport yyyy

where xxxx, yyyy are the tcp port numbers. Use 1955 and 1956 for example. The receiver for the bottom is open without arguments but still in the configuration file one needs to write n:flippeddatax 1, where 2n+1 indicated the half module number, 1 if it is a module.

Open as many receiver as half module boards. A single module has two half module boards.

From the software version 3.0.1, one can decide weather start a zmq callback from the receiver to the client (for example to visualize data in the slsDetectorGui or another gui). If the zmq steam is not required (cased of the command line for example, one can switch off the streaming with ./sls\_detector\_put rx\_datastream 0, enable it with ./sls\_detector\_put rx\_datastream 1. In the case of inizialising the stream to use the slsDetectorGui, nothing needs to be taken care of by the user. If instead you want to stream the streaming on different channels, the zmq port of the client can be set stealing from the slsDetectorGui stream having ./sls\_detector\_put zmqport 300y. Note that if this is done globally (not for every half module n independently, then the client automatically takes into account that for every half module, there are 2 zmq stream. The receiver stream ./sls\_detector\_put rx\_zmqport 300y has to match such that the GUI can work. If one desires to set the zmqport manually, he offset has to be taken into account: ./sls\_detector\_put 0:rx\_zmqport 300y, ./sls\_detector\_put 1:rx\_zmqport 300y+2 and so on..

There is an example code that can be compiled in manual/manual-api/mainReceiver.cpp and gives the executable ./detReceiver, use it with two or more receivers to open all receivers in one single terminal: ./detReceiver startTCPPort numReceivers withCallback, where startTCPPort assumes the other ports are consecutively increased.

#### 1.4 Mandatory setup - Client

The command line interface consists in these main functions:

sls\_detector\_acquire to acquire data from the detector

sls\_detector\_put to set detector parameters

sls\_detector\_get to retrieve detector parameters

First, your detector should always be configured for each PC that you might want to use for controlling the detector. All the examples given here show the command 0-, which could be omitted for the EIGER system 0. In the case more EIGER systems are controlled at once, the call of 1-,.. becomes compulsory.

To make sure the shared memory is cleaned, before starting, one should do:

sls\_detector\_get 0-free

To do that:

sls\_detector\_put 0-config mydetector.config

In the config file, if client, receiver and detector are using **1GbE** the following lines are mandatory (see slsDetectorsPackage/examples/eiger\_1Gb.config):

detsizechan 1024 512 #detector geometry, long side of the module first hostname beb059+beb058+ #1Gb detector hostname for controls 0:rx\_tcpport 1991 #tcpport for the first halfmodule 0:rx\_udpport 50011 #udp port first quadrant, first halfmodule 0:rx\_udpport2 50012 #udp port second quadrant, first halfmodule 1:rx\_tcpport 1992 #tcpport for the second halfmodule 1:rx\_udpport 50013 #udp port first quadrant, second halfmodule 1:rx\_udpport2 50014 #udp port second quadrant, second halfmodule rx\_hostname x12sa-vcons #1Gb receiver pc hostname outdir /sls/X12SA/data/x12saop/Data10/Eiger0.5M threaded 1

In the config file, if client, receiver and detector commands are on 1Gb, but detector data to receiver are sent using **10GbE** the following lines are mandatory (see slsDetectorsPackage/examples/eiger\_10Gb.config):

detsizechan 1024 512 #detector geometry, long side of the module first hostname beb059+beb058+ #1Gb detector hostname for controls 0:rx\_tcpport 1991 #tcpport for the first halfmodule 0:rx\_udpport 50011 #udp port first quadrant, first halfmodule 0:rx\_udpport2 50012 #udp port second quadrant, first halfmodule 0:rx\_udpip 10.0.30.210 #udp IP of the receiver over 10Gb 0:detectorip 10.0.30.100 #first half module 10 Gb IP 1:rx\_tcpport 1992 #tcpport for the second halfmodule 1:rx\_udpport 50013 #udp port first quadrant, second halfmodule 1:rx\_udpport2 50014 #udp port second quadrant, second halfmodule 1:rx\_udpip 10.0.40.210 #udp IP of the receiver over 10Gb, can be the same or different from 0:rx\_udpip

1:detectorip 10.0.40.101 #second half module 10 Gb IP rx\_hostname x12sa-vcons #1Gb receiver pc hostname outdir /sls/X12SA/data/x12saop/Data10/Eiger0.5M threaded 1

In the case you are developing your own receiver, then you need to remove the 1Gb receiver hostname rx\_hostname and substitute it with the mac address of the device:

```

configuremac 0

rx_udpmac xx:xx:...

```

One can configure all the detector settings in a parameter file setup.det, which is loaded by doing:

```

sls_detector_put 0-parameters setup.det

```

In the case of EIGER, the proper bias voltage of the sensor has to be setup, i.e. the setup.det file needs to contain the line vhighvoltage 150. Other detector functionality, which are rarely changed can be setup here. Other important settings that are configured in the setup.det file are:

- tengiga 0/1, which sets whether the detector is enabled to send data through the 1 or the 10 Gb Ethernet.

- flags parallel/nonparallel, which sets whether the detector is set in parallel acquisition and readout or in sequential mode. This changes the readout time of the chip and affects the frame rate capability (faster is parallel, with higher noise but needed when the frame rate is > 2 kHz.

- dr 32/16/8/4 sets the detector in autosumming mode (32 bit counter or not autosumming, 12 bit out of the chip). This is strictly connected to what is required for the readout clock of chip. See next point.

- clkdivider 0/1/2. Changes the readout clock: 200, 100, 50 MHz (also referred to as full, half, quarter speed). Note that autosumming mode (dr 32 only works at clkdivider 2=quarter speed). By selecting Refer to readout timing specifications in section5 for how to set the detector.

- flags continuous/storeinram. Allows to take frame continuously or storing them on memory. Users should use the continuous flags. Enabling the stroreinram flag makes the data to be sent out all at the end of the acquisition. Refer to readout timing specifications in section 5 for how to set the detector. Examples will be given in section ??.

One should notice that, by default, by choosing the option dr 32, then the software automatically sets the detector to clkdivider 2. By choosing the option dr 16, the software automatically sets the detector to clkdivider 1. One needs to choose clkdivider 0 after setting the dr 16 option to have the fastest frame rate. We would recommend expert users (beamline people) to write their parameters file for the users.

## 2 API versioning

The eigerDetectorServer running on the boards has a versioning API scheme that will make it crash if used with a wrong firmware. You can also check your versioning by hand with the code:

```

sls_detector_get softwareversion

```

gets the server (slsDetectorSoftware) version (answer is something like: softwareversion 111920160722.

```

sls_detector_get thisversion

```

returns the client version. The answer can be this version 111220160718.

```

/sls_detector_get detectorversion

```

returns the firmware version. The answer can be detectorversion 11. Killing and starting the server on the boards allows you to check the firmware version you have and also if your board is a top/bottom/master/slave.

## 3 Setting up the threshold

```

sls_detector_put 0-trimen N xxxx yyyy zzzz

sls_detector_put 0-settings standard

sls_detector_put 0-threshold energy_in_eV standard

```

The first line requires to specify how many (N) and at which energies in eV {ttxxxx, yyyy, zzzz and so on) trimmed files were generated (to allow for an interpolation). This line should normally be included into the mydetector.config file and should be set for you by one of the detector group. NORMALLY, in this new calibration scheme, only settings standard will be provided to you, unless specific cases to be discussed. The threshold at 6000 eV, for example would be set as:sls\_detector\_put 0-threshold 6000 standard.

For EIGER, at the moment normally only standard settings are possible. lowgain, verylowgain, veryhighgain and highgain are theoretically possible, but we never calibrate like this. They could be implemented later if needed.

Notice that setting the threshold actually loads the trimbit files (and interpolate them between the closest calibration energies) so it is time consuming. The threshold is expressed in (eV) as the proper threshold setting, i.e. normally is set to 50% of the beam energy.

We have added a special command, thresholdnotb, which allows to scan the threshold energy without reloading the trimbits at every stage. One can either keep the trimbits at a specific value (es.32 if the range of energies to scan is large) or use the trimbits from a specific energy (like a central energy).

sls\_detector\_put O-thresholdnotb energy\_in\_eV

### 4 Standard acquisition

After you setup the setting and the threshold, you need to specify the exposure time, the number of real time frames and eventually how many real time frames should be acquired:

```

sls_detector_put 0-exptime 1[time_is_s]

sls_detector_put 0-frames 10

sls_detector_put 0-period 0[time_is_s]

```

In this acquisition 10 consecutive 1 s frames will be acquired. Note that period defines the sum of the acquisition time and the desired dead time before the next frame. If period is set to 0, then the next frame will start as soon as the detector is ready to take another acquisition.

You need to setup where the files will be written to

```

sls_detector_put 0-outdir /scratch

sls_detector_put 0-fname run

sls_detector_put 0-index 0

```

this way your files will all be named /scratch/run\_dj.i.raw where j is relative to each specific half module, i in the index starts from 0 when starting the detector the first time and is automatically incremented. The next acquisition index will be 1. One can reset the index to what wished.

To acquire simply type:

```

sls_detector_acquire 0-

```

Note that acquiring is blocking. You can poll the status of the detector with:

```

sls_detector_get status

```

If the detector is still acquiring, the answer will return running. If the detector has finished and ready for the next acquisition, then it will return idle. You can also ask for the status of the receiver, to know when it has returned and finished getting the data with:

```

sls_detector_get receiver

```

There is a more complex way of performing an acquisition, that is useful for debugging and in case one wants a non blocking behavior:

You can then reset to zero the number of frames caught, then start the receiver and the detector:

- 1. sls\_detector\_put 0-resetframescaught 0

- 2. sls\_detector\_put 0-receiver start

- 3. sls\_detector\_put 0-status start

You can poll the detector status using:

#### sls\_detector\_get 0-status

When the detector is idle, then the acquisition is done but the receiver could still be receiving data. If you want, you can check if the receiver is finished receiving as many frames as you were expecting (this is optional but required for many many frames acquisition or when using some delays to send data at very high frame rate.

#### 4. sls\_detector\_get framescaught

Then you can stop the receiver as well now:

#### 5. sls\_detector\_put 0-receiver stop

The detector will not accept other commands while acquiring. If an acquisition wishes to be properly aborted, then:

#### • sls\_detector\_put 0-status stop

this same command can be used after a non proper abortion of the acquisition to reset to normal status the detector.

### 5 Readout timing- maximum frame rate

IMPORTANT: to have faster readout and smaller dead time, one can configure clkdivider, i.e. the speed at which the data are read, i.e. 200/100/50 MHz for clkdivider 0/1/2 and the dead time between frames through flags parallel, i.e. acquire and read at the same time or acquire and then read out. The configuration of this timing variables allows to achieve different frame rates. NOTE THAT IN EIGER, WHATEVER YOU DO, THE FRAME RATE LIMITATIONS COME FROM THE NETWORK BOTTLENECK AS THE HARDWARE GOES FASTER THAN THE DATA OUT.

In the case of REAL CONTINUOUS readout, i.e. continuous acquire and readout from the boards (independent on how the chip is set), the continuous frame rates are listed in table 1. Note that in the continuous flag mode, some buffering is still done on the memories, so a higher frame rate than the proper real continuous one can be achieved. Still, this extra buffering is possible till the memories are not saturated. The number of images that can be stored on the DDR2 on board memories are listed in table 2.

The maximum frame rate achievable with 10 GbE, dr 16, flags continuous, flags parallel,clkdivider 0, 6.1 kHz. This is currently limited by the connection between the Front End Board and the Backend board. We expect the 32 bit mode limit, internally, to be 2 kHz (clkdivider 2). In dynamic range dr 8 the frame rate is 11 kHz and fordr 4 is 22 kHz. For 4 and 8 bit mode the frame rate are directly limited by the speed of the detector chip and not by the readout boards.

| GbE | dynamic range | continuos maximum frame rate(Hz) | minimum period $(\mu s)$ |

|-----|---------------|----------------------------------|--------------------------|

| 1   | 16            | 256                              | 3901                     |

| 1   | 32            | 128                              | 7820                     |

| 10  | 16            | 2560                             | 391                      |

| 10  | 32            | 1280                             | 782                      |

| 10  | 8             | 5120                             | 196                      |

| 10  | 4             | 10240                            | 98                       |

Table 1: Frame rate limits for the CONTINUOS streaming out of images, i.e. the data rate out is just below 1Gb/s or 10Gb/s.

| dynamic range | images |

|---------------|--------|

| 4             | 30000  |

| 8             | 15000  |

| 16            | 7600   |

Table 2: Amount of images that can be stored on board. As while we store them, we start to send them out, the effective number of images could be larger than this, but it will depend on the network setup (how fats you stream out images).

# 5.1 Minimum time between frames and Maximum frame rate

We need to leave enough time between an exposure and the following. This time is a combination of the time required by the chip, by the readout boards and eventually extra time to reduce some appearance of cross talk noise between the digital and analog parts of the chip. It is essential to set the period of the detector, defined as the exptime plus an extra time, that needs to be at least the chip/board readout time. If this is set wrong (it is < exptime plus chip/board readout time), then the detector takes the minimum time it can, but you are in a not controlled frame rate situation.

The expected time difference between frames given by the pure chip readout time is in Table 3.

The period is s is defined as:

$$period = exptime + minimum time between frames$$

(1)

where the 'minimum time between frames' and the minimum period will be discussed in Table 4.

As if you run too fast, the detector could become noisier, it is important to match the detector settings to your frame rate. This can be done having more parameters files and load the one suitable with your experiment. We experienced that with low energy settings could not reach 6 kHz and no noise.

| dr | clkdivider | expected chip readout $t(\mu s)$ | measured chip readout $t(\mu s)$ |

|----|------------|----------------------------------|----------------------------------|

| 4  | 0          | 41                               | 40                               |

| 4  | 1          | 82                               | 84                               |

| 4  | 2          | 123                              | 172                              |

| 8  | 0          | 82                               | 82                               |

| 8  | 1          | 164                              | 167                              |

| 8  | 2          | 328                              | 336                              |

| 12 | 0          | 123                              | 122                              |

| 12 | 1          | 246                              | 251                              |

| 12 | 2          | 491                              | 500                              |

Table 3: Readout time required from the chip to readout the pixels. The numbers are obtained using equation 5.

| dr | clkdivider | flags       | t between frames(μs) | max frame rate (kHz) | min period (µs)    | max imgs (nominal/our network) |

|----|------------|-------------|----------------------|----------------------|--------------------|--------------------------------|

| 4  | 0          | parallel    | 3.4                  | 22                   | 44                 | 30k/50k                        |

| 4  | 1          | parallel    | 6                    | 10.5                 | 92                 | 30k/100k                       |

| 4  | 2          | parallel    | 11.2                 | 5.4                  | 197                | infinite                       |

| 8  | 0          | parallel    | 3.4                  | 11.1                 | 89                 | 15k/24k                        |

| 8  | 1          | parallel    | 6.1                  | 5.7                  | 181                | 15k/52k                        |

| 8  | 2          | parallel    | 11.2                 | 2.9                  | 342                | infinite                       |

| 16 | 0          | parallel    | 3.4                  | 6.1                  | $(126+38)^* = 164$ | 8k/12k                         |

| 16 | 0          | nonparallel | 126                  | 5.6                  | $(126+52)^* = 179$ | 8k/23k                         |

| 16 | 1          | parallel    | 6.1                  | 3.9                  | 257                | 8k/28k                         |

| 16 | 1          | nonparallel | 255                  | 3.3                  | 303                | infinite                       |

| 16 | 2          | parallel    | 11                   | 1.9                  | 526                | infinite                       |

| 16 | 2          | nonparallel | 504                  | 1.8                  | 555                | infinite                       |

Table 4: Readout settings. The  $_{\rm min\ exptime}$  possible is  $5-10\ \mu s$ . This is due to the time to pass the pixel enable signal in the whole chip. The time between frames has been measured with the oscilloscope and the maximum frames rate has been tested with an external gating from a pulse generator at known frequence. The minimum period is obtained as  $1/\max$  frame rate.

In 16 bit mode, it could make sense, in case of noise and low threshold to either reduce the frame rate:

new period = exptime + minimum time between frames +

$$(10-20 \mu s)$$

(2)

to let the signal settle or, if the frame rate is important, leave the period at the same value but reduce the exptime:

new exptime = old exptime -

$$(10-20 \ \mu s)$$

(3)

In general, choose first the desired dead time: this will tell you if you want to run in parallel or non parallel mode, although most likely it is parallel mode. Then, choose the maximum frame rate you want to aim, not exceeding what you aim for not to increase the noise. In 4 and 8 bit modes it makes no sense to run nonparallel as the exposure time is too small compared to the readout time.

#### 5.1.1 4 and 8 bit mode

In parallel mode, the minimum time between frames is due to the time required to latch the values of the counter with capacitors. These values are determined in firmware and they can be estimated as:

time between frames, parallel =

$$4\mu s \cdot (clkdivider + 1)$$

(4)

This time is independent on the dr.

In nonparallel mode, it is easily possible to calculate the required asic readout time. Indeed a block of (8\*256) pixels are readout, the bits pixel are the dr and the speed of readout is 5ns/bit \*(clkdivider+1):

asics readout time =

$$5ns/bit \cdot 2^{(clkdivider+1)} \cdot dr \cdot (8*256) + 4\mu s \cdot (clkdivider+1)$$

(5)

While we expose the next frame, we still need to readout the previous frame, so we need to guarantee that the period is large enough at least to readout the frame. So the maximum frame rate has to be  $1/(asic\ readout\ time)$ . The minimum period has to be equal to the asic readout time.

#### 5.1.2 16 bit mode

A similar situation happens in 16 bit mode, where this is more complicated because of three things:

- 1. The chip actual dr is 12 bit

- 2. The chip is readout as 12-bit/pixel, but the FEB inflates the pixel values to 16-bits when it passes to the BEB. This means that effectively the FEB to BEB connection limits the data throughput in the same way as if the dr of the chip would really be 16 bits.

| dr | clkdivider | flags       | t difference between subframes $(\mu s)$ | max internal subframe rate (kHz) | maximum frame rate (Hz) |

|----|------------|-------------|------------------------------------------|----------------------------------|-------------------------|

| 32 | 2          | parallel    | 12                                       | 2                                | 170                     |

| 32 | 2          | nonparallel | 504                                      | < 2                              | 160                     |

Table 5: Timing for the 32bit case. The maximum frame rate has been computed assuming 2 subframes of default subexptime of 2.62144 ms.

3. While in 4 and 8 bit mode it makes no sense to run in nonparallel mode as the exptime/dead time ratio would be not advantageous, in 16 bit mode, one can choose how to run more freely.

If we are in parallel mode, the dead time between frames, is also here described by equation 4. If we are in nonparallel mode, the dead time between frames is defined by 5 ONLY for clkdivider 1 and 2. So the maximum frame rate has to be 1/(chip readout time) in this case. Only for clkdivider 0 we hit some limitation in the bandwidth of The FEB  $\rightarrow$  BEB connection. In this case, the maximum frame rate is lowered compared to what expected.

#### 5.1.3 32 bit mode

The autosumming mode of Eiger is the intended for long exposure times (frame rate of order of 100Hz, PILATUS like). A single acquisition is broken down into many smaller 12-bit acquisitions, each of a subexptime of 2.621440 ms by default. Normally, this is a good default value to sustain an intensity of  $10^6$  photons/pixel/s with no saturation. To change the value of subexptime see section 7.

The time between 12-bit subframes are listed in table 5.

The exposure time brokend up rounding up to the full next complete subframe that can be started. The number of subframes composing a single 32bit acquisition can be calculated as:

$$\# \text{ subframes} = (int)(\frac{\text{exptime (s)}}{\text{subexptime (s)} + \text{difference between frames (s)}} + 0.5)$$

(6

This also means that exptime < subexptime will be rounded to subexptime. If you want shorter acquisitions, either reduce the subexptime or switch two 16-bit mode (you can always sum offline if needed).

The UDP header will contain, after you receive the data, the effective number of subframe per image (see section 10.1) as "SubFrame Num or Exp Time", i.e. the number of subframes recorded (32 bit eiger). The effective time the detector has recorded data can be computed as:

effective exptime = (subexptime)

$$\cdot$$

(# subframes) (7)

In the future release, a configurable extra time difference between subframes will be introduced for the parallel mode, so that some noise appearing in detectors at low threshold can be removed. This will enlarge the time difference

Figure 3: **Trigger INPUT** (looking at a single module from the back, top) is the **rightmost**, **down**.

between frames form the default 12  $\mu$ s to something configurable, expected to be 15-40  $\mu$ s (for the 9M it is currently 200  $\mu$ s due to a noisier module).

### 6 External triggering options

The detector can be setup such to receive external triggers. Connect a LEMO signal to the TRIGGER IN connector in the Power Distribution Board (see Fig.). The logic 0 for the board is passed by low level 0-0.7 V, the logic 1 is passed to the board with a signal between 1.2-5 V. Eiger is 50  $\Omega$  terminated. By default the positive polarity is used (negative should not be passed to the board).

```

sls_detector_put 0-timing [auto/trigger/burst_trigger/gating]

sls_detector_put 0-frames x

sls_detector_put 0-cycles y

sls_detector_acquire 0-

```

No timeout is expected between the start of the acquisition and the arrival of the first trigger.

Here are the implemented options so far:

- auto is the software controlled acquisition (does not use triggers), where exptime and period have to be set. Set number of cycles (i.e. triggers) to 1 using cycles. Set number of frames using frames.

- trigger 1 frame taken for 1 trigger. Your frames needs to be 1 always, cycles can be changed and defines how many triggers are considered. exptime needs to be set. In the GUI this is called trigger exposure series.

- burst\_trigger gets only 1 trigger, but allows to take many frames. With frames one can change the number of frames. cycles needs to be 1. exptime and period have to be set. In the gui it is called trigger readout.

- gating allows to get a frame only when the trigger pulse is gating. Note that in this case the exp time and period only depend on the gating signal. cycles allows to select how many gates to consider. Set number of frames to 1 using frames.

Hardware-wise, the ENABLE OUT signal outputs when the chips are really acquiring. This means that the single subframes will be output in 32 bit mode. The TRIGGER OUT outputs the sum-up-signal at the moment (which is useless). This will be changed in the future to output the envelop of the enable signal.

We are planning to change some functionality, i.e. unify the trigger and burst trigger modes and make both frames and cycles configurable at the same time.

#### 7 Autosumming and rate corrections

In the case of autosumming mode, i.e, dr 32, the acquisition time (exptime is broken in as many subframes as they fit into the acquisition time minus all the subframes readout times. By default the subexptime is set to 2.621440 ms. This implies that 12 bit counter of EIGER will saturate when the rate is above or equal to 1.57 MHz/pixel. The minimum value is of order of 10 ns (although as explained values smaller than 500  $\mu$ s do not make sense). The maximum value is 5.2 s.

The subframe length can be changed by the user by doing:

sls\_detector\_put 0-subexptime [time\_in\_s]

One needs to realize that the readout time, for each subframe is 10.5  $\mu$ s if the detector is in parallel mode. 500  $\mu$ s if the detector is in non parallel mode. Note that in dr 32, as the single frame readout from the chip is 500  $\mu$ s, no subexptime<500  $\mu$ s can be set in parallel mode. To have smaller subexptime, you need the nonparallel mode, although this will have a larger deadtime than the acquisition time.

Rate corrections are possible online (and the came procedure can be used offline) by creating a look-up table between the theoretically incident counter value  $c_i$  and the detected counter value  $c_d$ . In the EIGER on board server, this look-up table is generated assuming that the detected rate  $n_d$  can be modeled as a function of the incident rate  $n_i$  according to the paralyzable counter model:

$$n_d = n_i \cdot exp(-n_i \cdot \tau), \tag{8}$$

where  $\tau$  represents an effective parameter for the dead time and the loss in efficiency. The look-up table is necessary as we are interested to obtain  $c_i(c_d)$

and equation 8 is not invertible. One needs to notice that the paralyzable counter model to create a look-up tables applies only if photons arrive with a continuous pattern (like at the SLS). If photons are structured in fewer but intenser bunches, deviations may arise. This is the case for some operation modes at the ESRF. For those cases we are studying how to correct, probably from a simulated correction tables if an analytical curve cannot be found. In the new calibration scheme,  $\tau$  is given as a function of the energy. It is loaded from the trimbit files and interpolation between two trimbit files are performed. One needs to make sure the appropriate  $\tau$  value is written in the trimbit files, then need to load the appropriate settings and vthreshold before.

Online rate corrections can be activated for dr=32. They are particularly useful in the autosumming mode as every single subframe is corrected before summing it. To correct for rate, the subframe duration has to be known to the correction algorithm. Rate corrections for dr=16 will be activated as well in the next firmware release. To activate the rate corrections, one should do:

```

sls_detector_put 0-ratecorr [tauval_in_ns]

To deactivate:

```

```

sls_detector_put 0-ratecorr 0

```

Now to activate the rate corrections with the value written in the trimbit file or interpolated from there, once would do:

```

sls_detector_put 0-ratecorr -1

```

Every time either the rate corrections are activated,  $\tau$  is changed or the subframe length is changed, then a new correction table is evaluated. Note that computing the correction table is time consuming.

## 8 Dependent parameters and limits

Here is a list of dependent parameters:

dr changes clkdivider: dr 16 → clkdivider 1. You can change it to (0, 1, 2); the frame rate changes accordingly to table 4. Setting the dr to 32 changes clkdivider to 2. Only way dr 32 can work.

Here is a list of "ignored" parameters, meaning that if the parameters are not what the detector expects, it will ignore them, but there is no guarantee that you get what you think you are asking:

1. **period**. Assuming that you set the correct **exptime** according to the table 4, the **period** to be used by the detector has to be >= **exptime**+readout time (table 4). Otherwise the detector will take data at the minimum possible period, which is **exptime**+readout times. **period** is not changed by the detector after the acquisition.

Here is a list of limits that should be checked:

- 1. If **dr** is 32 and **clkdivider** is not 2, whatever the detector gets out is wrong (the boards cannot properly keep up)

- 2. If the variable **frames** is greater than what the memory can store (table 2) and the frame rate exceed the continuos streaming (table 1), limits on the maximum number of images need to be implemented if the period is lower than the one listed in table 1. Check table 4 to see the different cases.

- 3. Running at a speed that does not support the frame rate you are asking: see table 4 to check if the frame rate (**period**) you are asking is compatible with the **clkdivider** you are asking.

- 4. Running at a readout time that does not support the frame rate you are asking. Check table 4 to check if the frame rate (**period**) you are asking is compatible with the **flags** you are asking.

- 5. The minimum allowed value for **exptime** should be 10  $\mu$ s.

- 6. By default the **subexptime** is set to 2.621440 ms. Values smaller than 500  $\mu$ s do not make sense. The maximum value is 5.2 s. This limits should be checked.

Here is a list of parameters that should be reset:

- 1. **resetframescaught** should be reset to zero after every acquisition taken with receiver start, status start, receiver stop. If the acquisition is taken with sls\_detector\_acquire, there is no need to reset this.

- 2. After changing the timing mode of the detector, one should reset to '1' the unused value, in that specific timing mode, between **frames** and **cycles**. See section 6 for how to use the timing. At the present moment the detector will acquire more frames than planned if the variable not used between **frames** and **cycles** is not reset. In future releases, the unused variable will be ignored. Still resetting is a good practice.

## $9 ext{ } 1\text{Gb/s}, 10\text{Gb/s links}$

#### 9.1 Checking the 1Gb/s, 10Gb/s physical links

LEDs on the backpanel board at the back of each half module signal:

- the 1Gb/s physical link is signaled by the most external LED (should be green). For top half modules is at the extreme left. For bottom half modules is at the extreme right.

- the 10Gb/s physical link is signaled by the second most external LED next to the 1Gb/s one (should be green).

Figure 4: 1 and 10GB LEDs position.

# 9.2 Delays in sending for 1Gb/s, 10Gb/s, 10Gb flow control, receiver fifo

Extremely advanced options allow to:

- Activate the flow control for 10 Gb/s E (by default the 1 Gb/s E is always active and cannot be switched off:

- ./sls\_detector\_put flowcontrol\_10g 1

- Delay the transmission of the left port. This delay option is useful in the case of many simultaneous receivers running, such that it reduces the throughput to the receivers all at the same time. To be used board by board (i.e X:, Y:,etc.. with different units:

- ./sls\_detector\_put X:txndelay\_left xxxx

- Transmission delay of the right port, same as above. The value here should be different from the left port to spread the transmission even more

- ./sls\_detector\_put X:txndelay\_right yyyy

As example:

for X in \$(seq 0 4); do ./sls\_detector\_put \$X:txndelay\_left \$((X\*100000)); done

```

./sls_detector_put X:txndelay_right ((X*100000)); X=$((X+1)); done

```

• Set transmission delay of the entire frame. This is required as you want to finish sending the first frame to all receivers before starting sending the second frame to the receivers with shorter delay time. This value has to be greater than the maximum of the transmission delays of each port.

```

./sls_detector_put txndelay_frame zzzz

```

In the example before, it would be: zzzz=4\*100000+ 100000

• Readjust the size of the fifo of the receiver between listening and writing (useful when writing is limited)

```

./sls_detector_put rx_fifodepth xxxx

```

xxxx is 100 images by default.

• Deactivate a half module (for ROI or debugging). Note that the MASTER module SHOULD NOT be deactivated:

```

./sls_detector_put X:activate 0

```

where X is the half module you want to deactivate. The receiver at this point will return fake data (overflow) for this module. If you wish to eliminate the receiver overall for this module, then you need to run a configuration file where this module has been removed. To activate back a module, do:

```

./sls_detector_put X:activate 1

```

#### 9.3 Setting up 10Gb correctly: experience so far

For configuring well the 10Gb card not to loose packets,

- MTU must be set up to 9000 (jumbo frames) on all the involved sides: detector, switch, server NIC

- you should set up static MAC address tables with separated VLANs

As root, also do:

```

ethtool -G xth1 rx 4096, ethtool -C xth1 rx-usecs 100

```

where xth1 can be replaced with the correct 10Gb device. To minimise loosing packets, priorities are set better as root user, so have the receiver as root. To try to bypass being root, we trued something like this:

```

/etc/security/limits.conf username rtprio 99

```

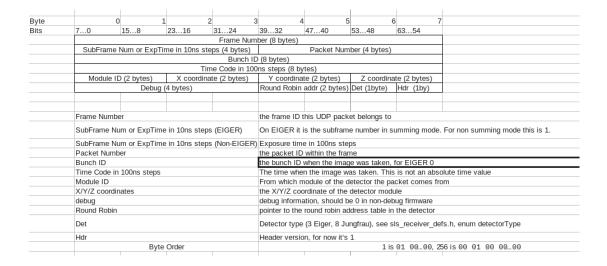

Figure 5: UDP header out of EIGER

but somehow it did not fully worked so we kept the trick of being root.

Very important is to activate the flow control in 10Gb (in 1Gb it is on by default and not configurable)

#### ./sls\_detector\_put flowcontrol\_10g 1

Set the transmission delays as explained in the manual.

It can help to increase the fifo size of the receiver to rx\_fifodepth to 1000 images

#### ./sls\_detector\_put rx\_fifodepth 1000

One needs to keep into account that in 16 bit mode for 1 image we expect each slsReceiver to allocate 0.5MB. So for 1000 images, we expect 500MB memory for each receiver. This can be monitored in Linux with "top" or "free -m".

## 10 Offline processing and monitoring

#### 10.1 Data out of the detector: UDP packets

The current UDP header format is described in figure 5.

#### 10.2 Data out of the slsReceiver

For a module, the geometry of the ports are as in table 6: white the option n:flippeddatax 1, which flips in vertical the content of the module. By convection, we usually use 1:flippeddatax 1, but one could flip the top instead.

| 0:rx_udpport | 50011 | 0:rx_udpport2 | 50012 |

|--------------|-------|---------------|-------|

| 1:rx_udpport | 50013 | 1:rx_udpport2 | 50014 |

Table 6: UDP port geometry for a single module, 4 UDP ports.

#### 10.3 "raw" files

If you use the option of writing raw files, you will have a raw file for each UDP port (meaning most likely 2 chips), 4 files per module. In addition to the raw files, you will get also a "master" file, containing in ascii some detector general parameters and the explanation of how to interpret the data from the raw files.

The master file is named: filename\_master\_O.raw and for version "3.0" of the slsDetectorSoftware looks like:

Version : 1.0

Dynamic Range : 16

Ten Giga : 1

Image Size : 262144 bytes

x : 512 pixels

y : 256 pixels

Total Frames : 1

Exptime (ns) : 1000000000 SubExptime (ns) : 2621440 Period (ns) : 1000000000

Timestamp : Thu Aug 17 10:55:19 2017

#### #Frame Header

Frame Number : 8 bytes SubFrame Number : 4 bytes Packet Number : 4 bytes Bunch ID : 8 bytes Timestamp : 8 bytes Module Id : 2 bytes X Coordinate : 2 bytes Y Coordinate : 2 bytes Z Coordinate : 2 bytes Debug : 4 bytes Round Robin Number: 2 bytes : 1 byte Detector Type Header Version : 1 byte

Note that if one wants to reconstruct the real time the detector was acquiring in 32 bit (autosumming mode), one would have to multiply the SubExptime (ns) for the SubFrame Number.

#### 10.4 Offline image reconstruction

The offline image reconstructionslsImageReconstruction is not part of the package anymore.

The detector writes 2 raw files per receiver. An offline image reconstruction executable has been written to collate the possible files together and produce cbf files. The executable uses the CBFlib-0.9.5 library (downloaded from the web as it download some architecture dependent packages at installation). At cSAXS, the CBFlib-0.9.5 has been compiled -such that the required packages are downloaded in /sls/X12SA/data/x12saop/EigerPackage/CBFlib-0.9.5.

To use it for a single module:

```

cbfMaker [filename with dir]

```

```

eg. cbfMaker /scratch/run_63_d1_f00000000000_3.raw

```

To use it for a 1.5 multi modules:

```

cbfMaker [filename] [pixels x] [pixels y] ([singlemodulelongside_x] [start det])

```

eg. cbfMaker /scratch/run\_63\_d0\_f000000000000\_3.raw 3072 512 1 0. The [singlemodulelongside\_x] [option to interpolate gap pixels] param are optional. Defaults are "1", the detector long side is on the x coordinate and start to reconstruct from module 0. The executables:

```

bcfMaker1.5M [file_name_with_dir]

bcfMaker9M [file_name_with_dir]

```

-1 at the present time.

contain the hardcoded geometry for the 1.5M (3 modules horizontal on the long side) and for the 9M at cSAXS:  $6(\text{short side}) \times 3$  (long side) modules. Missing packets in a frame and border pixels ( $\times 2$  and  $\times 4$  are given with value

It is important to know, that the pixels at the edge between 2 chips count more as double size. We can virtually introduced 1 virtual pixel per double larger pixel, so to have an even number of counts everywhere. Virtual pixels (not filled ) between module gaps are also inserted.

```

GapPixelsBetweenChips_x = 2;

GapPixelsBetweenChips_y = 2;

GapPixelsBetweenModules_x = 8;

GapPixelsBetweenModules_y = 36;

```

#### 10.5 Read temperatures/HV from boards

With an updated kernel on the linux boards (ask to the SLS detector group for specifications), it is possible to monitor the temperature on the boards:

```

temp_fpga

#gets the temperature of the fpga

temp_fpgaext

#gets the temperature close to the fpga

temp_10ge

#gets the temperature close to the 10GE

temp_dcdc

#gets the temperature close to the dc dc converter

temp_sodl

#gets the temperature close to the left so-dimm memory

temp_sodr

#gets the temperature close to the right so-dimm memory

temp_fpgafl

#gets the temperature of the left front end board fpga

#gets the temperature of the right front end board fpga

temp_fpgafr

```

You need to use the command specifying from which board you desire the temperature readings, for example:

```

./sls_detector_get 0:temp_fpga

./sls_detector_get 1:temp_fpga

```

In 500k–2M pixel systems there is a hardware temperature safety switch, which will cut power to the BEBs when reaching a too high temperature. For the 9M system, there is a temperature sensor read by the bchip100 PCU which will shutdown the detector when above a certain temperature.

The HV can also be set and read through the software:

```

./sls_detector_put vhighvoltage 150

./sls_detector_get vhighvoltage

```

./eigerDetectorServer &

Note that the get vhighvoltage would return the measured HV from the master module only. If getting the vhighvoltage for individual halfmodules, only the master will have a value different from -999.

# A Kill the server, copy a new server, start the server

All the below operations are form a terminal and assume you login to the boards. Kill current server:

```

ssh root@bebxxx #password is root killall eigerDetectorServer # kill server and stopserver Copy a new version of the server (if necessary, otherwise skip it): cd executables scp user@pc:/path/eigerDetectorServerNewVersion . chmod 777 eigerDetectorServerNewVersion mv eigerDetectorServerNewVersion eigerDetectorServer sync Start the server again:

```

Note that the server appropriate for the software version used is located inside the package: slsDetectorsPackage/serverBin/eigerDetectorServerxx.yy...

To copy the detector server on many boards, a script can be implemented on the lines of:

```

for i in beb111 beb070;

do ssh root@$i killall eigerDetectorServer;

scp eigerDetectorServer root@$i:~/executables/eigerDetectorServer ;

ssh root@$i sync; done

```

## B Loading firmware bitfiles

A **bcp** executable (which needs **tftp** installed on the PC, is needed.

- 1. Manual way: you need to press something on the detector. To program bitfiles (firmware files), do a hard reset with a pin/thin stuff in the holes at the very back of the module. They are between the top 7 LED and the bottom 1 and opposite for the other side. Push hard till all LEDs are alternating green and red.

- 2. Software way (possible only if you have the correct programs copied on your board. If not, as the sls detector group).

```

ssh root@bebxxx

cd executables

./boot_recovery

```

In both case, after booting, only the central LED should be on green and red alternating.

From a terminal, do:

```

nc -p 3000 -u bebxxx 3000

```

where xxx is the board number. It is enough top monitor with nc only one board. Pres enter twice (till you see a prompt with the board hostname printed) and keep this terminal to monitor. It takes a bit of time to load the bitfiles, but the terminal tells you.

From another terminal you do:

```

./bcp feb_left.bit bebxxx:/febl

sleep 300; #or till the screen over netcat has told you Successful

./bcp feb_right.bit bebxxx:/febr

sleep 300; #or till the screen over netcat has told you Successful

./bcp download.bit bebxxx:/fw0

sleep 300; #or till the screen over netcat has told you Successful

```

If you need to program a new kernel (only needed when told to do so):

```

./bcp kernel_local bebxxx:/kernel sleep 300; #or till the screen over netcat has told you Successful

```

do the same for the other boards. You can program in parallel many boards, but you cannot load two bitfiles on the same board till loading and copying one process has finished. So load all left febs together, then proceed to the right febs, then the bebs. Power off completely everything. Power it on.

## C Pulsing the detector

There are two ways to pulse the detector:

• Pulse digitally: when you are interested to the output readout and do not care about the analog response from the pixels:

```

sls_detector_put vthreshold 4000

sls_detector_put vtr 4000

sls_detector_put pulsechip N #to pulse N

sls_detector_put pulsechip -1 #to get out of testing mode

```

Note that the answer will be  $2 \cdot N + 2$  in this case.

• Pulse analogically: You want to really check the analogical part of the detector, not just the readout.

```

sls_detector_put vcall 3600

sls_detector_put vthreshold 1700

sls_detector_put vrf 3100

for i in $(seq 0 7);

do px=$((-255+i));

sls_detector_put pulse 0 $px 0;

for j in $(seq 0 255); do

sls_detector_put pulsenmove N 0 1;

done;

done;

sls_detector_p resmat 0

sls_detector_acquire

```

You read N in every pixel if you are setup correctly.

## D Load a noise pattern with shape

For debug purposes, we have created a noise pattern with a shape. If you reconstruct correctly your image, you should be able to read ".EIGER" in the same direction for both the top and bottom in normal human readable orientation. To load the special noise file look at settingsdir/eiger/standard/eigernoise.sn0xx in the package.

### E Troubleshooting

#### E.1 Cannot successfully finish an acquisition

#### E.1.1 Only master module return from acquisition

When no packets are received AND detector states in 'running status'. Widest list of causes. Query the status of each half module till the maximum number N, for i in \$(seq 0 N); do sls\_detector\_get \$i:status; done, to check if there are half modules that are still running.

If only the master modules return but ALL the other half modules do not:

- FEB LED 1 and or 3 become red while trying to acquire an image: reconnect or change the DDR2 memories. Technically it is a FIFO problem to communicate the data to the rest of the chain.

- It can be that the master cable is not connected, check.

- It can be that the synchronization cable is not connected or the termination board at the synchronization does not work. Check.

#### E.1.2 A few modules do not return from acquisition

If only a few modules are still running but the others return, it is a real problem with a backend board or a synchronization bug. If you can, ssh into the board, kill and start the eigerDetectorServer again (see Section A for how to do this). Keep the terminal with the output from the eigerDetectorServer and repeat the acquisition.

- Check if the acquisition returned from the server or not. In case seek help from the SLSDetectorGroup.

- In the server you read something along the lines of "cannot read top right address". It is communication between the front and backend board. Or FEB FPGA is not programmed. Try to program again FPGA, and make sure you program FPGA bit files 70x, if you have 70x FPGAs, or 30x, if you have 30x FPGAs. If still fails, tell the SLSDetectorGroup as it could be a hardware permanent failure.

#### E.2 No packets (or very little) are received

In both cases running wireshark set to receive UDP packets on the ethernet interface of the receiver (filter the UDPport>=xxxx, where xxxx is written in the configuration file) can help you understanding if NO packets are seen or some packets are seen. You have to set the buffer size of the receiving device in wireshark to 100Mbyte minimum. If no packets are received, check that your

receiving interface and detector UDPIPs are correct (if in 10Gb). Most of the time in this case it is a basic configuration problem. It can help looking at the receiver output, shown in an example here:

Missing Packets : 224064

Complete Frames : 3499

Last Frame Caught : 3499

The Last Frame Caught, meaning the packet from the last frame that was sent out by the detector, can help in understanding the problem:

- If some packets are received, but not all, it could be a network optimization problem. In this case, the Last Frame Caught will be a value close to the expected number of frames with missing frames distributed over the whole frame range. In this case:

- For receiving data over 1Gb, the switch must have FLOW CONTROL enabled

- If using 10GbE, check that the 10Gb link is active on the backpanel board. Then refer to Section 9.3 to see how to configure the 10Gb ports on the receiving machine correctly.

- 2. If the Last Frame Caught value is much lower than the expected frames and you are missing a bunch of frames from a point onwards, and you are using receiver start, status start: then it can be that you are stopping the receiver too early. In particular when you are using delay it might be that there is some time between when the detector is already done and in idle state but the receiver is still receiving data. Check with ./sls\_detector\_get framescaught if the receiver is already done before doing ./sls\_detector\_put receiver stop.

- 3. If the Last Frame Caught value is much lower than the expected frames and you are missing a bunch of frames from a point onwards and you are running at a higher frame rate than the continuous framerate (see table 1) with more images than the size of the memory (see table 2). It might be that you are running out of memory to store images. There is no protection for this. see point E.3

#### E.3 'Got Frame Number Zero from Firmware'

In this case, you have run out of memory size (see table 2 for the size) on the boards so you are trying to store on the DDR2 memories more images that they can contain and the network is not fast enough to send everything out from the 10GbE. So if you see:

Got Frame Number Zero from Firmware. Discarding Packet

it means that you run out of memory at the previous acquisition. The cure is taking 2 or 3 SINGLE images in a raw to clear out the memories.

# E.4 The module seems dead, no lights on BEBs, no IP addresses

- Check the 2 fuses on the power distribution board. If one of the fuses is in shortcuircuit, then exchange it. Nominal values are 7 A and 5 A. Old modules with 5 A and 3 A could trip.

- The module is not properly cooled and the temperature safety switch has killed the power to the backend boards.

#### E.5 The module seems powered but no IP addresses

If the 1G LED (see Section 9.1) on the backpanel board is not green:

- Check that the 1Gb cable is plugged in.

- Check that there is a DCHP server assigning IP addresses to the board.

- The IP address is assigned only at booting up of the boards. Try to reboot in case the board booted before it could have an IP address.

- Check that you did not run out of IP addresses

Check that the board is not in recovery mode (i.e. the central LED on the back is stable green, see Fig 4). In this case reboot the board with the soft reset or power cycle it.

If the 1Gb LED on the backpanel board is green (see Section 9.1):

• Check that the IP address has been refreshed on the PC you are trying to communicate to the detector from. Run on the PC as root the following command to update the DNS cache: nscd -i hosts

#### E.6 Receiver cannot open socket

It is connected to the TCPport which the receiver uses:

- The port is already in use by the same receiver already opened somewhere

or by another process: check with ps -uxc your processes

- In rare cases, it might be that the TCP port crashes. To find out which process uses the TCPPOrt do: **netstat -nlp grep xxxx**, where xxxx is the tcpport number. To display open ports and established TCP connections, enter: **netstat -vatn**. Kill the process.

#### E.7 The client ignores the commands

Make sure that in the configuration file you do not have lock 1 activated, as this will let only one username from one IP address talk to the detector. To deactivate it, you need to run lock 0 from the client session where you locked it.

#### E.8 Zmq socket is blocked

It is connected to the TCPport which is used. In rare cases, it might be that the TCP port crashes. To find out which process uses the TCPPOrt do: **netstat**-nlp — **grep** xxxx, where xxxx is the tcpport number. To display open ports and established TCP connections, enter: **netstat** -vatn. Kill the process.

#### E.9 Client has shmget error

Note that occasionally if there is a shared memory of a different size (from an older software version), it will return also a line like this:

```

*** shmget error (server) ***-1

```

This needs to be cleaned with ipcs -m and then ipcrm -M xxx, where xxx are the keys with nattch 0. Alternative in the main slsDetectorFolder there is a script that can be used as sh cleansharedmemory.sh. Note that you need to run the script with the account of the client user, as the shared memory belongs to the client. It is good procedure to implement an automatic cleanup of the shared memory if the client user changes often.

#### E.10 Measure the HV

For every system:

- Software-wise measure it (now the software returns the measured value), with sls\_detector\_get vhighvoltage. The returned value is the HV (for proper Eiger setting is approximately 150 V) if it is correctly set. If two master modules are presents (multi systems), the average is returned (still to be tested). If one asks for the individual n half module bias voltage through sls\_detector\_get n:vhighvoltage, if the n module is a master, the actual voltage will be returned. If it is a slave, -999 will be returned.

- Hardware-wise (opening the detector) measure value of HV on C14 on the power distribution board. Check also that the small HV connector cable is really connected.

The 2M system at ESRF has a HV enable signal that needs to be shortcut in order to overwrite vacuum protections (when not in vacuum). The 1.5M for OMNY has a relay system that enables HV only when the vacuum is good. For both systems, it makes sense not to set the HV while running the configuration file but set it at a later stage when sure about the vacuum.

#### E.11 The image now has a vertical line

Check if the vertical line has a length of 256 pixels and a width of 8 columns. In this case it is a dataline being bad. It can be either a wirebond problem or a frontend board problem. try to read the FEB temperature (see Section ??) and report the problem to the SLSDetector group. Most likely it will be a long term fix by checking the hardware.

#### E.12 The image now has more vertical lines

If you see strange lines in vertical occurring at period patterns, it is a memory problem. The pattern is 4 columns periodic in 16 bit mode, 8 columns periodic in 8 bit mode and 2 columns periodic in 32 bit mode. Try to switch on and off (sometimes it is a strange initialization problem).

#### E.13 ssh to the boards takes long

Depending on your network setup, to speed up the ssh to the boards from a pc with internal dhcp server running: iptables -t nat -A POSTROUTING -o eth1 -j MASQUERADE; echo "1" ; /proc/sys/net/ipv4/ip\_forward, where eth1 has to be the 1Gb network device on the pc

#### E.14 Check firmware version installed on BEB

You can either ask in the client as described in section 2, or login to the boards directly. Follow some steps described in Section A.

```

ssh root@bebxxx #password is root

killall eigerDetectorServer # kill server and stopserver

cd executables/

./eigerDetectorServer&

```

Scroll up in the terminal till you find Firmware Version: xx

# E.15 Check if half-module is a master, a slave, a top or a bottom

Follow some steps described in Section A.

#### E.16 'Cannot connect to socket'

This error is typically due to the detector server not running. For why, see section E.17.

#### E.17 Detector server is not running

The detector server could not be running: either the detector was powered off, or it powered off itself due to too high temperature or, in the case of the 9M, if the waterflow sensor detected no flux and powered it off (the chiller stops occasionally as cSAXS).

If the powering and the temperature are OK, instead, it can be that the firmware version is incompatible to the server version and/or the client software version. So check the consistency of firmware/software/server versions.

#### E.18 'Acquire has already started' error message

If you see the client returning the following error message:

"Acquire has already started. If previous acquisition terminated unexpectedly, reset busy flag to restart.(sls\_detector\_put busy 0)"

You need to run the command:

./sls\_detector\_put busy 0

#### E.19 There is noise running the detector in 32-bit

Short story (for now): You are running in parallel mode, switch flags to non nonparallel mode. Long story: If you are running the detector in 32-bit (autosumming), there might be some noise, particularly at lower thereshold energies. This is due to the fact that the analog part of the chips require some latency time to settle which is larger than the redout time. At the present moment it is possible to run the detector only in parallel or nonparallel mode, respectively with readout times between frames of 12  $\mu$ s and 504  $\mu$ s. If you switch flags to non nonparallel mode you will give enough time for teh signals to settle. For future realeas we are planning to introduce some configurable delay, such that you can remain with the parallel flag, but can obtain a configurable dead time between frames in the range 12-504  $\mu$ s.

# E.20 There is noise running the detector at high frame rate(4,8,16 bit)

If are running in parallel mode, in particular at low thereshold energies, you might encounter some noise. The reason is that the analog part of the chips require some latency time to settle which is larger than the redout time.

1. You can lower the frame rate and relax requirements on period: At low frame rate, you normally leave enough time between the end of the acquisition and the starting of the next, so you should not see this effect. In any case setting a period=exptime+readout time from Table 3 +extra  $20\mu$ s cures the problem. The  $20\mu$ s could also be  $10~\mu$ s, they are very hardware dependent.

2. The frame rate requirement are stingent (as for time resolved measurements): the only option here is to reduce the exptime to let the extra  $20 \mu s$  (or  $10) \mu s$ . The period remains the same.

#### F Client checks - command line

Guide on returned strings:

#### 1. sls\_detector\_get free

Returns a list of shared memories cleaned (variable number depending on detector):

```

Shared memory 273612805 deleted

Shared memory 276922374 deleted

Shared memory 270270468 deleted

free freed

```

Note that occasionally if there is a shared memory of a different size (from an older software version), it will return also a line like this:

```

*** shmget error (server) ***-1

```

This needs to be cleaned with ipcs -m and then ipcrm -M xxx, where xxx are the keys with nattch 0.

2. sls\_detector\_get settings settings standard

standard is only if correct. undefined or anything else is wrong.

3. sls\_detector\_get threshold

threshold xxxx

Returns a string (xxxx) that can be interpreted as the threshold in eV. If it fails to set it, returns the last threshold it was set (which the detector still has). If settings are not defined or different trimbits are chosen, it will return "undefined".

- 4. sls\_detector\_get fname fname string